IEDM 2019:英特尔披露Lakefield芯片与Foveros技术新进展

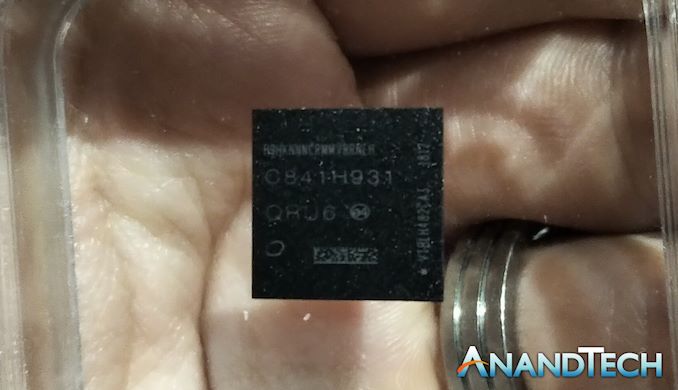

(题图 via AnandTech)

其想法是使用多个彼此叠置的硅芯片,且其中一个硅芯片专门用于高速缓存或内存,以减小芯片的总体封装尺寸、同时增加贷款。

作为英特尔首款 Foveros 芯片(Lakefield),其堆叠了采用不同制程节点的芯片,包括一个 I/O 和计算裸片、以及附加的 PoP 内存。

目前已宣布的两款 Lakefield 产品,分别是三星 Galaxy Book S 和微软的 Surface Neo,预计上市时间为 2020 年中。

第二款 Foveros 芯片,是基于 Xe -HPC 架构的高性能计算 GPU 。其代号为“Ponte Vecchio”,计划于 2021 下半年发布,并将使用 Foveros 技术,每个 GPU 将具由两部分硅芯片组合而成。

该 GPU 主要为百亿级别的 Aurora 超级计算机而打造,后者将于 2021 年安装在阿贡国家实验室。

在 IEDM 2019 的舞台上,英特尔首席工程师还表示:2020 年假日季,我们有望见到 Lakefield 市场的一些更新。初代产品已经面世(尚未开放预订),详情要等到 2020 年底的第二代更新。

外媒猜测,采用堆叠设计的芯片,或支持下一代 PCIe 等新 I/O,并迎来内核优化平衡后的高效率新计算芯片。

随着时间的推移,英特尔显然会将其 Foveros 和 EMIB 互联工艺作为其产品组合(至少在某些领域)的基石。至于成本能否拉低到对价格更敏感的市场,仍有待观察。

最后,在同一场 IEDM 演示中,工程师还提到 Foveros 堆栈技术可整合调制解调器中。鉴于英特尔最近刚宣布与联发科合作,新技术或在 5G 时代发挥更大的用场。

相关标签

相关文章

王慧文病休53天,旗下OneFlow团队重新创业

1年以前 | 1次阅读

智己CEO现场怒怼!不满LS6和小鹏G6当对手

1年以前 | 1次阅读

董明珠回应落榜世界500强:总比爆雷的世界500强好

1年以前 | 1次阅读

阿里云上线 AI 视频生成工具 Live Portait:可一键让照片开口说话

1年以前 | 78次阅读

妙鸭相机将并入神力视界,阿里大文娱CTO郑勇:不是“搬家”是“回家”

1年以前 | 85次阅读

特斯拉上海超级工厂约40秒下线一台车,零部件本土化率超95%

1年以前 | 69次阅读

宁德时代发布神行超充电池,可实现充电10分钟行驶800里

1年以前 | 71次阅读

中科院博士被骗到缅甸已一年!女友:他负债几万,家里条件一般,以为去当翻译

1年以前 | 85次阅读

小鹏汽车否认收购玛莎拉蒂传闻:系谣言

1年以前 | 63次阅读

联想二季度净利润猛降66%,股价应声跳水

1年以前 | 80次阅读

业内人士:视觉中国对不同侵权主体采用差异化策略,老客由销售沟通新客发律师函

1年以前 | 70次阅读

恒大集团在美国申请破产保护

1年以前 | 56次阅读

劳斯莱斯首款纯电轿跑将在北美亮相

1年以前 | 89次阅读

realme印度前CEO确认加盟荣耀,即将推出手机新品

1年以前 | 88次阅读

OpenAI正在测试内容审核系统,一天可以完成六个月的工作

1年以前 | 80次阅读

谷歌百人“复仇者联盟”出击,将发对标GPT-4的大模型,26位研发主管名单流出

1年以前 | 77次阅读

OpenAI收购数字产品公司Global Illumination,为创立以来首笔公开收购

1年以前 | 80次阅读

海口规定:电动汽车充电服务费不得超过0.65元每度

1年以前 | 80次阅读

波音任命柳青为波音中国总裁

1年以前 | 88次阅读

业内人士谈图片复杂代理链:图片代理商越多摄影师分成越少

1年以前 | 67次阅读